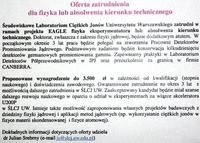

Projekt urządzenia do badań naukowych, dość ambitny, zajęcie prawie na 2 lata.

Realizacja w Warszawie, ale nie wykluczałbym możliwości pracy zdalnej.

To nie jest robota dla jednej osoby - nie ma szans, by sobie z tym poradziła w tym czasie

- dlatego trzeba będzie pracować zespołowo, i trzeba do tego umieć pracować w zespole.

Zbieranie danych przychodzących jako sygnały analogowe, mają być przetwarzane przez szybkie ADC

(AD9640 14 bit 150 MHz), na cyfrowe, które będą wstępnie obrabiane i selekcjonowane na FPGA (Virtex

FX20) i na koniec przesyłane przez Ethernet (raczej gigabitowy) na komputery. Częstotliwości nieco

niższe od największych, jakie są w PC (FX20 ma używać pamięci DDR, wystarczy DDR200).

Raczej nie będzie lutowania, może sporadycznie - montaż będzie SMD, zlecimy go jakiejś firmie.

Głównie potrzebna jest wiedza (i trzeba będzie się douczać) i posługiwanie się komputerem.

Konieczna umiejętność czytania (i to dość biegłego) dokumentacji elementów po angielsku.

Oceniamy, że powinien sobie z tym poradzić absolwent wydziału elektroniki na politechnice.

Trzeba będzie projektować płytki drukowane (w Eagle, ale profesjonalnym - zakupiliśmy, płytki będą

10-16 warstwowe; można w czymś innym, np. KiCad, który jest darmowy, powinien się nadawać -

tylko pod Eagle są definicje elementów, których zamierzamy używać, a pod KiCad-a może nie być),

i poradzić sobie z obudową BGA (572 piny co 1 mm w kwadracie 25x25mm, więc dość ciasno);

dobrać elementy i ich rozmieszczenie tak, by ADC (inne elementy też) działały stabilnie (lepiej, żeby

zmiany temperatury nie powodowały zmiany odczytów z ADC ani wadliwego działania układów).

Prawdopodobnie istotne będą opóźnienia w propagacji sygnałów po ścieżkach płytki drukowanej -

może trzeba będzie dodawać linie opóźniające, żeby wyrównać opóźnienia między sygnałami.

Cały projekt ma być własnością instytutu (Środowiskowe Laboratorium Ciężkich Jonów, UW) -

może z zastrzeżeniem, że pracujący nad nim mogą go wykorzystywać potem do innych prac -

ale ŚLCJ musi mieć prawo jego wykorzystywania bez ograniczeń.

Po uruchomieniu tego systemu będziemy potrzebowali elektronika do konserwacji systemu, może

- jeśli będą chętni - będziemy dalej to rozwijać. Nie mam informacji, ile będzie można zarabiać

podczas pracy nad projektem; o ile pamiętam, dla elektronika do konserwacji może być do 4000zł

na miesiąc; z doświadczeniem uzyskanym podczas pracy na tym projektem można gdzie indziej

zarobić ze 2 razy tyle - ludzie z tego typu doświadczeniem są bardzo poszukiwanie przez firmy.

Realizacja w Warszawie, ale nie wykluczałbym możliwości pracy zdalnej.

To nie jest robota dla jednej osoby - nie ma szans, by sobie z tym poradziła w tym czasie

- dlatego trzeba będzie pracować zespołowo, i trzeba do tego umieć pracować w zespole.

Zbieranie danych przychodzących jako sygnały analogowe, mają być przetwarzane przez szybkie ADC

(AD9640 14 bit 150 MHz), na cyfrowe, które będą wstępnie obrabiane i selekcjonowane na FPGA (Virtex

FX20) i na koniec przesyłane przez Ethernet (raczej gigabitowy) na komputery. Częstotliwości nieco

niższe od największych, jakie są w PC (FX20 ma używać pamięci DDR, wystarczy DDR200).

Raczej nie będzie lutowania, może sporadycznie - montaż będzie SMD, zlecimy go jakiejś firmie.

Głównie potrzebna jest wiedza (i trzeba będzie się douczać) i posługiwanie się komputerem.

Konieczna umiejętność czytania (i to dość biegłego) dokumentacji elementów po angielsku.

Oceniamy, że powinien sobie z tym poradzić absolwent wydziału elektroniki na politechnice.

Trzeba będzie projektować płytki drukowane (w Eagle, ale profesjonalnym - zakupiliśmy, płytki będą

10-16 warstwowe; można w czymś innym, np. KiCad, który jest darmowy, powinien się nadawać -

tylko pod Eagle są definicje elementów, których zamierzamy używać, a pod KiCad-a może nie być),

i poradzić sobie z obudową BGA (572 piny co 1 mm w kwadracie 25x25mm, więc dość ciasno);

dobrać elementy i ich rozmieszczenie tak, by ADC (inne elementy też) działały stabilnie (lepiej, żeby

zmiany temperatury nie powodowały zmiany odczytów z ADC ani wadliwego działania układów).

Prawdopodobnie istotne będą opóźnienia w propagacji sygnałów po ścieżkach płytki drukowanej -

może trzeba będzie dodawać linie opóźniające, żeby wyrównać opóźnienia między sygnałami.

Cały projekt ma być własnością instytutu (Środowiskowe Laboratorium Ciężkich Jonów, UW) -

może z zastrzeżeniem, że pracujący nad nim mogą go wykorzystywać potem do innych prac -

ale ŚLCJ musi mieć prawo jego wykorzystywania bez ograniczeń.

Po uruchomieniu tego systemu będziemy potrzebowali elektronika do konserwacji systemu, może

- jeśli będą chętni - będziemy dalej to rozwijać. Nie mam informacji, ile będzie można zarabiać

podczas pracy nad projektem; o ile pamiętam, dla elektronika do konserwacji może być do 4000zł

na miesiąc; z doświadczeniem uzyskanym podczas pracy na tym projektem można gdzie indziej

zarobić ze 2 razy tyle - ludzie z tego typu doświadczeniem są bardzo poszukiwanie przez firmy.