delgo napisał: Zrobiłem jak pisał Driver, odłączyłem wejście sygnału do LM7001 i podłączyłem sterowanie nap. warikapów przez potencjometr. Przy ok.2,2V miałem f=132MHz a przy ok.7,2 f=136MHz to by było z zapasem dla odbioru i ok.11,5 f=146. Ponownie podłączyłem zgodnie ze schematem, nie zaskoczyła...

Myślę że podanie częstotliwości ze skanera nie ma co sprawdzać, podejrzewam że wynik będzie negatywny, zakres przestrajania jest Ok i powinna była zaskoczyć o ile się wyrabia powyżej 130MHz.

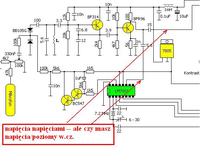

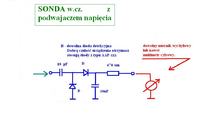

delgo napisał: nawet po zwiększeniu c 5,6p na 15p na wejściu sygnału na LM. Napięcie na wej LM to ok. 2,2V (sonda).

Ustaw na wejściu FMIN ~1,5V w.cz. z sondy. Już powyżej 0,1V powinna działać prawidłowo, bez potrzeby nie ma co zwiększać napięcia na wejściu FMIN. Bo może go braknąć do wysterowania następnych stopni nadajnika.

delgo napisał: Mam wątpliwości czy poprawnie zaprogramowałem ATmegę w bascom ustawienia są sztywne dla kwarca do 8 MHz zewnętrzny (001100) a w programie odwołuje się konkretnie do 7,2MHz.

Jak pisałeś masz dwa zaprogramowane µC, więc na którymś powinno zadziałać. Sama ATmega działa bo wyświetla częstotliwość na wyświetlaczu. A jeśli nawet w programie sztywno ustawione jest 8MHz to może mieć wpływ co najwyżej na częstotliwość tonu 1750Hz. Nie programowałem w BASCOM'ie ale wiem że program symuluje pracę µC i jeśli coś jest nie tak to zgłosił by błędy przed kompilacją do pliku hex. Ale zastanawia mnie co innego mianowicie pętla FOR dla ustawień B0,B1,B2,TB,R0,R1,R2,S. W programie zadeklarowana jest stała "Sterowanie = &B10100000 '25 kHz", która wysyłana jest w pętli

For A = 0 To 7 ' wysyłanie bitów sterujących LM7001

If Sterowanie.a = 1 Then ' B0,B1,B2,TB,R0,R1,R2,S

Set Portd.0

Else

Reset Portd.0

End If

Call Zegarek ' po każdym bicie takt zegara

Next A

Po sprawdzeniu warunku "If Sterowanie.a = 1" jeśli zostanie spełniony wysyłana jedynka przez "Set Portd.0", lub zero przez "Reset Portd.0" jeśli warunek zwróci fałsz. W datasheet LM7001 podana jest kolejność w ramce po bitach dla dzielnika częstotliwości D0-D13 i dwóch bitach testowych T0 i T1 powinny być wysłane bity B0,B1,B2,TB,R0,R1,R2,S. Z tego co wiem pętla "FOR A=0 TO 7" wykonywana jest tak że zmiennej "A" przypisywana jest wartość po znaku równości, sprawdzany jest warunek czy "A" przekroczyła wartość końcową, wykonywane są rozkazy w pętli, zmienna A zwiększana jest o 1 i pętla zaczyna się od początku. W momencie przekroczenia zadanej wartości po "TO" pętla kończy działanie, wiec rozkazy zawarte w pętli wykonają się dokładnie 8 razy. Nasuwa mi się pytanie jaka jest kolejność bitów przypisywana ze stałej "Sterowanie". Są dwie możliwości pierwsza bity są wysyłane kolejno po &B do końca wartości więc przypisanie wyglądało by tak B0=0, B1=1, B2=0, TB=0, R0=0, R1=0, R2=0, S=0 to ustawia dzielnik referencyjny na 100kHz oraz przestawia wejście dzielnika na AMIN. Nawet jak po podziale z dzielnika częstotliwości VCO jest 25kHz, to występuje różnica w dzieleniu częstotliwości referencyjnej 100kHz i VCO i 25KHz. Ponadto do dzielnika VCO nic nie dochodzi bo sygnał z VCO podany jest na FMIN a nie na AMIN jak zostało ustawione. Mamy więc krach syntezy.

Druga mozliwość i ta była by prawidłowa jeśli &B było by końcem zmiennej "Sterowanie" a ostatni znak z rzędu przypisywany jako pierwszy, wtedy przypisanie wyglądało by tak B0=0, B1=0, B2=0, TB=0, R0=0, R1=1, R2=0, S=1. Wtedy dla sygnału z VCO ustawione jest dla dzielnika wejście FMIN, na które faktycznie jest sygnał podany, mamy po dzielniku referencyjnym 25kHz, zatem częstotliwości z obu dzielników w którymś momencie się zrównają na 25kHz, a synteza zaskoczy i będzie trzymać. Może w tych ustawieniach coś jest nie tak, spróbuj zadeklarować stałą "Sterowanie = &B00000101". O ile mój tok myślenia jest prawidłowy, całkiem możliwe że synteza saskoczy.

delgo napisał: Na PW miałem dwie odpowiedzi na ten temat i dotyczyły tego samego cewki jak największa dobroć , ekranowanie i tym zajmę się na początek

Duża dobroć cewki ma wpływ na poziom napięcia w obwodzie rezonansowym i stabilniejszą częstotliwość, więc wyższy i stabilniejszy sygnał na wyjściu generatora. Natomiast ekranowanie zapobiega głównie sprzężeniom pasożytniczym, które przy nadawaniu mogły by powodować wzbudzenie nadajnika na przypadkowych częstotliwościach. Nawet przy braku ekranowania synteza powinna zaskoczyć.