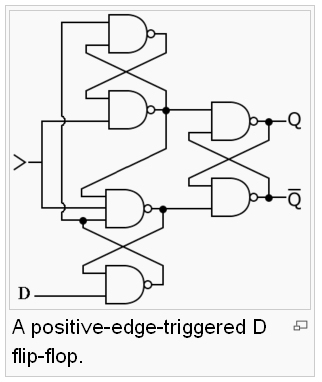

Przerzutnik D to właściwie przerzutnik RS z dodanym układem próbkującym. Zależnie od potrzeb sygnał D może być próbkowany na przednim lub tylnym zboczu sygnału C.

Przykład rozwiązania (nieminimalny ale działający)

Bramki U1A i U1B tworzą przerzutnik RS ustawiany albo z bramek U1C i U2A albo z wejść R i S (po inwerterach U3E i U3F odwracających stany R i S by było jak w przerzutnikach D układu 4013)

Bramki U1C i U2A są bramkami próbkującymi stan wejścia D (i D zanegowane po U3A). W momencie ich otwarcia, stan wejścia D ustawia odpowiednio przerzutnik wyjściowy U1A/U1B

Przerzutnik U2B/U2C oraz inwertery U3B i U3D tworzą generator impulsu próbkującego sterującego bramkami U1C i U1B.

Generacja ta polega na wytworzeniu dwóch przebiegów (w punktach A i B) przesuniętych w czasie o sumę czasów propagacji U3B, U2B i U3D

Gdy C=1 to A=0 a B=1,

Gdy C=1->0 to najpierw A=1 i B=1 -> następuje próbkowanie wejścia D

Po czasie propagacji U3B, U2B i U3D B=0 i kończy się próbkowanie wejścia D.

Gdy C=0 to A=1 i B=0.

Gdy C=0->1 to A=0, B=0 - próbkowanie nie następuje

Po opóźnieniu A=0, B=1 - próbkowanie nie następuje

C_111111111000000000000001111111111 <- zegar C

A_000000000111111111111110000000000 <-sygnał A

B_111111111110000000000000011111111 <-sygnał B

P_000000000110000000000000000000000 <-próbkowanie wejścia D

Układ powyższy do celów poglądowych nie do kopiowania w celach ocenowych

Dodano po 16 [minuty]: [quote="dir3ctor"]Czyli po nastapieniu sekwencji clocka 1->0 wystawiamy na Q wartosc podana na D.

Tu masz błąd myślowy, bo w przerzutniku D wyzwalanym zboczem występuje niejawnie trzeci sygnał czyli zapamiętany stan wejścia C (dla celów wykrycia zbocza) czyli masz

C[t-1], C[t] i D[t]

C[t] jest przepisywane asynchronicznie do C[t-1]

Próbkowanie D[t] następuje gdy C[t-1] i C[t] są różne