Witam, chciałbym zrobić prosty ale skuteczny układ resetowania procków z podanych w temacie rodzin. Wiem że 51' resetuje sie sygnałem wysokim a AVR i ATMEGA sygnałem niskim.

Najprościej było by podłaczyc kondensator miedzy nóżką reset i + zasilania, ale takie rozwiązanie nie jest pewne, czasami zdarza się że procesor potrafi nie wstać, zbocza takiego sygnału są chyba za mało strome.

Istnieją co prawda gotowe rozwiązania w stylu 3 pinowych specjalizowanych resetorów (DSxxxx) - ale są drogie, czasami trudnodostępne a poza tym nie ma już tej przyjemności z ich stosowania co zbudować własny układ

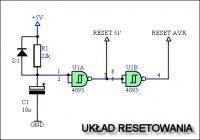

Po przejżeniu kilku schematów udało mi się narysować coś takiego jak w załączniku. Według mnie to powinno działać w nastepujący sposób: po włączeniu zasilania kondensator jest pusty, ładuje sie stosunkowo powoli przez resystor. W tym czasie powiedzmy że ustala sie napiecie zasilania z zasilacza od poziomu +5V, a procesor jest nieaktywny.

Po przekroczeniu pewnego progowego napięcia bramki (CD4093) NAND z histerezą (dlatego z histerezą - bo zwykły NAND mógłby błędnie reagować na powoli narastające napięcie na wejściu) bramka się przełącza, na jej wyjściu mamy czysty - ładny przebieg o ostrych zboczach. Jeżeli chce sie uzyskać sygnał zanegowany to trzeba go podać na wejście kolejnej bramki, która go odwróci.

Niech się ktoś wypowie co o tym sądzi i czy to bedzie działało w praktyce,

nie mam niestety oscyloskopu z pamięcią żeby zaobserwować tak szybkie zmiany sygnału, a nie jestem najlepszy z cyfrówki, tak więć wszelkie racjonalne wskazówki mile widziane

Zastanawiam też czy do procesrów ATMEGA wogóle potrzebny jest taki układ - słyszałem ze można ustawić im bitami Fuse autoreset bez zewnętrzych elementów .......

Najprościej było by podłaczyc kondensator miedzy nóżką reset i + zasilania, ale takie rozwiązanie nie jest pewne, czasami zdarza się że procesor potrafi nie wstać, zbocza takiego sygnału są chyba za mało strome.

Istnieją co prawda gotowe rozwiązania w stylu 3 pinowych specjalizowanych resetorów (DSxxxx) - ale są drogie, czasami trudnodostępne a poza tym nie ma już tej przyjemności z ich stosowania co zbudować własny układ

Po przejżeniu kilku schematów udało mi się narysować coś takiego jak w załączniku. Według mnie to powinno działać w nastepujący sposób: po włączeniu zasilania kondensator jest pusty, ładuje sie stosunkowo powoli przez resystor. W tym czasie powiedzmy że ustala sie napiecie zasilania z zasilacza od poziomu +5V, a procesor jest nieaktywny.

Po przekroczeniu pewnego progowego napięcia bramki (CD4093) NAND z histerezą (dlatego z histerezą - bo zwykły NAND mógłby błędnie reagować na powoli narastające napięcie na wejściu) bramka się przełącza, na jej wyjściu mamy czysty - ładny przebieg o ostrych zboczach. Jeżeli chce sie uzyskać sygnał zanegowany to trzeba go podać na wejście kolejnej bramki, która go odwróci.

Niech się ktoś wypowie co o tym sądzi i czy to bedzie działało w praktyce,

nie mam niestety oscyloskopu z pamięcią żeby zaobserwować tak szybkie zmiany sygnału, a nie jestem najlepszy z cyfrówki, tak więć wszelkie racjonalne wskazówki mile widziane

Zastanawiam też czy do procesrów ATMEGA wogóle potrzebny jest taki układ - słyszałem ze można ustawić im bitami Fuse autoreset bez zewnętrzych elementów .......